在接受日本媒体IT Media 采访时,英特尔日本负责人分享了公司在未来四年内重新夺回制程*地位的计划。

他表示。随着 Alder 和 Raptor Lake 的 7nm(Intel 7)节点问世,Meteor Lake 的 4nm(i4)晶圆已经量产。Intel 4 工艺将带来20% 的每瓦性能提升,并采用 EUV 光刻技术以获得更好的良率和密度。

他进一步指出。英特尔还准备在 2023 年底推出其 3nm 等效工艺节点。这些晶圆专为服务器级至强芯片设计。第 5 代 Xeon Emerald Rapids-SP 将采用 Intel 3 工艺制造。Emerald Rapids 将在 Sapphire Rapids 一年内作为软更新推出。值得一提的是,这将是最后一个采用 FinFET 晶体管的节点。

你可能想知道英特尔如何在六个月内量产两个节点。但其实按照报道,英特尔的4nm(intel 4)和 3nm(intel 3)工艺由两个独立的团队同时开发。这本质上是Tick Tock 模型的重新启动,允许快速节点采用。

由此可见,在14nm苦苦挣扎几年之后,英特尔将在今年进一步拉近和台积电和三星的差距,其IDM 2.0战略,也使得他们成为了3nm代工的一个重要玩家。

三星台积电先后跨入

和5nm一样,三星和台积电都率先进入了3nm时代。

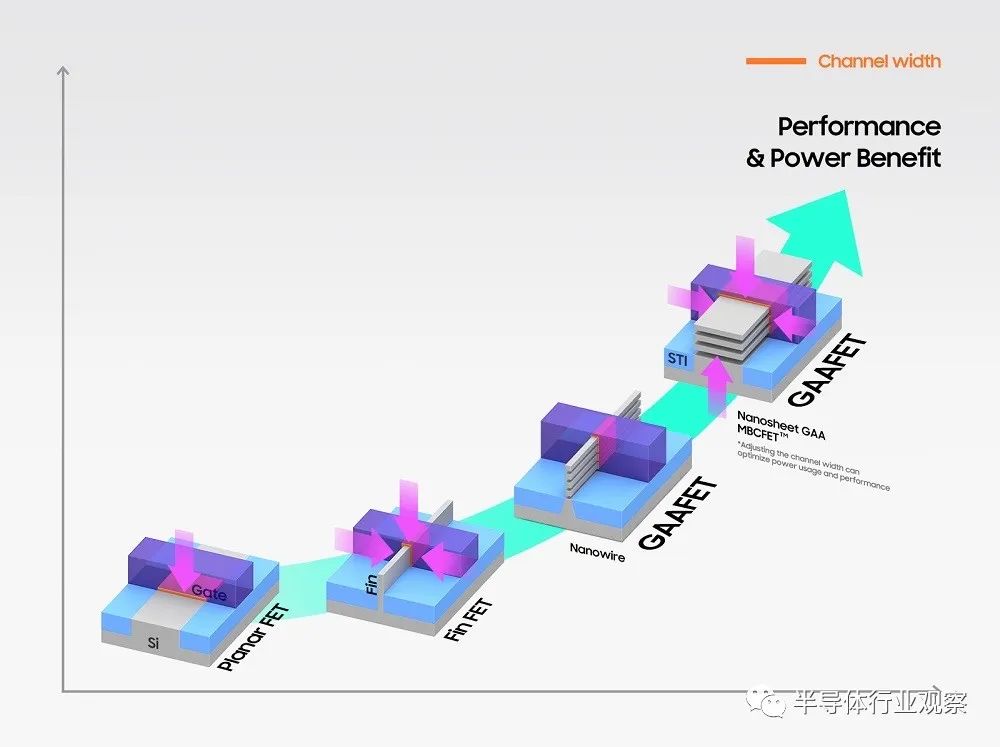

在2022年六月份,韩国巨头三星宣布,公司已开始了采用环栅 (GAA) 晶体管架构的3纳米 (nm) 工艺节点的初始生产。

三星表示,公司通过一个名为Multi-Bridge-Channel FET (MBCFET™) 的 GAA 技术,突破了 FinFET 的性能限制,通过降低电源电压水平提高功率效率,同时还通过增加驱动电流能力提高性能。

三星在新闻稿中谈到,通过公司专有技术利用了具有更宽通道的纳米片,与使用具有更窄通道的纳米线的 GAA 技术相比,三星的方案可实现更高的性能和更高的能效。也正是通过利用 3nm GAA 技术,三星将能够调整纳米片的通道宽度,以优化功耗和性能,以满足各种客户需求。

在三星看来,GAA 的设计灵活性非常有利于设计技术协同优化 (DTCO),这有助于提高功率、性能、面积 (PPA) 优势。而与5nm工艺相比,三星*代3nm工艺相比5nm功耗最高可降低45%,性能提升23%,面积减少16%,而第二代3nm工艺则功耗最高可降低50%,性能提高 30%,面积减少 35%。

自三星的这个3nm面世以来,围绕着这个技术有了很多的纷争,当中包括了客户和良率。但据韩国经济日报在去年11月的报道,这家韩国科技巨头正在与五到六家无晶圆厂客户共同开发先进芯片,最早将于 2024 年大量供应。消息人士称,三星将使用其 3 纳米技术为 Nvidia 制造图形处理单元 (GPU)、为 IBM 制造中央处理器 (CPU)、为高通制造智能手机应用处理器以及为百度制造用于云数据中心的人工智能芯片。

据知情人士在最近所说,现在三星的*代 3 纳米工艺节点的生产良率达到了“*水平”,但没有进一步详细说明。“我们现在正在毫不拖延地开发第二代 3nm 芯片,”知情人士告诉韩国经济日报。

紧随三星,晶圆代工龙头台积电在2022年年底也举行了盛大的庆祝仪式,重磅宣布公司的3nm量产。

台积电方面表示,公司的 3nm 技术 (N3) 将是继5nm 技术 (N5) 的又一次全节点跨越,并在推出时提供 PPA 和晶体管技术方面*进的代工技术。与 N5 技术相比,N3 技术将提供高达 70% 的逻辑密度增益、在相同功率下高达 15% 的速度提升以及在相同速度下高达 30% 的功率降低。N3 技术开发进展顺利。N3 技术将为移动和 HPC 应用程序提供完整的平台支持。

据semianalysis报道,N3 系列节点包括 N3B、N3E、N3P、N3X 和 N3S。其中许多是针对特定目的优化的小节点,但有所不同。(详细可以参考文章)

N3B即原来的 N3,与 N3E 无关。与其将其视为 nodelet,不如将其视为一个完全不同的节点。

在 IEDM 2022 上,台积电透露了 N3B 的一些方面。N3B 具有 45nm 的 CGP,与 N5 相比缩小了 0.88 倍。台积电还实施了自对准接触,从而可以更大程度地扩展 CGP。台积电还展示了 0.0199 μm2 的 6 晶体管高密度 SRAM 位单元。这仅缩小了 5%,这对于 SRAM 未来的扩展来说是个坏兆头。(详细内容请参考我们之前的文章)

semianalysis表示,与N5相比,台积电最初表示,N3在同等功率下性能提升约12%,同等性能下功耗降低27%。这将具有 1.2× SRAM 密度和 1.1× 模拟密度。

IEDM 上公开的高密度位单元仅将 SRAM 密度提高了约 5%,与最初声称的 20% 相去甚远。

在 IEDM 期间,台积电透露 N3B 的 CGP 为 45nm,是迄今为止透露的最密集的。这*于Intel 4的50nm CGP、三星4LPP的54nm CGP和TSMC N5的51nm CGP。

虽然逻辑密度的增加无疑是有希望的,但低 SRAM 密度增益意味着 SRAM-heavy 设计可能会经历显着的成本增加。N3B 的良率和金属堆叠性能也很差。

正是由于 N3B 未能达到 TSMC 的性能、功率和产量目标,因此他们开发了 N3E。其目的是修复N3B的缺点。*个重大变化是金属间距略有放松。台积电没有在触点、V1、V2、M0、M1 和 M2 金属层上使用多重图案化 EUV,而是退缩并切换到单一图案化。

至于3nm的用户,台积电魏哲家在日前的法说会上表示,公司3nm于去年第4季量产,高效能运算及智能手机客户需求超越供应能力,2023年将全产能生产。魏哲家说,升级版3纳米制程将于今年第3季量产。

魏哲家表示,3纳米及升级版3纳米今年合计将贡献中个数百分比(约4%至6%)营收,营收贡献将高于5纳米制程量产第1年的贡献,客户产品设计定案数量也将是5纳米的2倍以上。

从上述两大晶圆厂的数据可以看到,3nm似乎很受客户欢迎。相关统计更是指出,到 2025 年,3 nm 工艺节点市场预计将达到 255 亿美元,超过 5 nm 工艺的估计 193 亿美元 。

这也就难怪英特尔会在这个工艺上如此着紧。

英特尔来势汹汹

在基辛格重返英特尔担任CEO以后,他定下了雄心勃勃的IDM 2.0计划。

时任英特尔代工服务总裁 Randhir Thakur(现在已经离职)在去年11月接受日经亚洲采访时表示:“我们的目标是在本世纪末成为世界第二大代工厂,并且 [我们] 期望产生*的代工利润率”。

如上所说,3nm毫无疑问将成为英特尔的一个关键节点。

按照英特尔所说,Intel 3 将共享Intel 4 的一些特性,但足够新来描述这个新的完整节点,特别是新的高性能库。其每瓦性能比Intel 4 提高 18%。

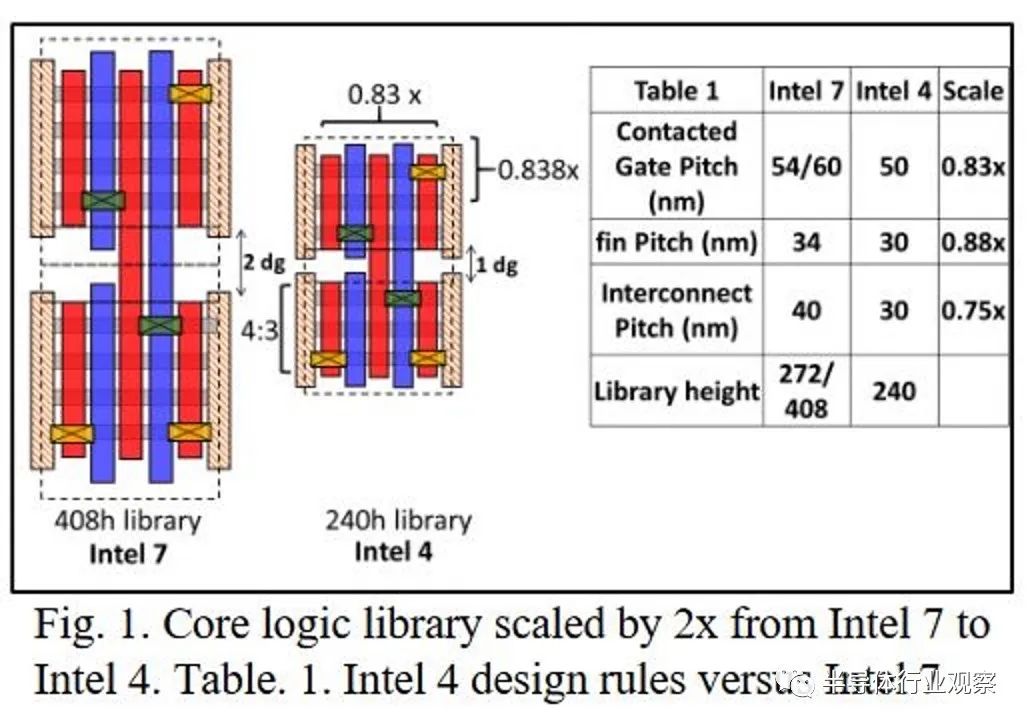

因为英特尔把intel 4当作intel 3的基础,外媒semiwiki也将其与台积电3nm比较,我们在这里介绍一下已经有更多消息披露的intel 4的工艺细节,以给大家对intel 3的期望提供更多参考。

据介绍,Intel 4 是相对于 Intel 7 的全节点缩减,在相同的功率范围内估计性能提高了 20%,或者在相同的时钟下功率降低了 40%。这是英特尔自重新启动其作为其他芯片设计商的客户代工厂以来宣布的*个全节点缩减,但该公司并不期望其新客户部署intel 4,尽管它强调他们将能够如果他们愿意,可以使用它。相反,英特尔认为,当该工艺可用时,其未来的前沿代工客户将主要瞄准intel 3,其原因之一是英特尔 4 针对高性能芯片进行了优化。

英特尔将在 Intel 4 工艺中将 EUV 引入制造,然后在 Intel 3 中深化该技术的使用。据英特尔称,在没有 EUV 的情况下,从Intel 7 到Intel 4,每个 CPU 需要使用的掩模数量将增加 30%。相反,Intel 4 所需的掩膜数量下降了 20%。总流程步骤减少了 5%。

与台积电一样,英特尔最初对 EUV 的采用将受到限制。据报道,该公司正在使用 EUV 进行接触,但仅限于某些金属层和通孔。台积电和三星都将 EUV 用于触点、通孔和金属层。预计英特尔将通过Intel 3 扩大其对 EUV 的采用,因此这种差距将随着时间的推移而缩小。

按照semiwiki在之前的报道中所说,英特尔所披露的Intel 4 的高性能单元密度约为Intel 7 的 2 倍。与Intel 4 相比,Intel 3 应该具有“更密集”的库。如果假设Intel 3 的间距相同但轨道高度更小,那么与Intel 10/7相比,得到的高性能单元密度约为 1.07 倍,高密度单元的密度约为 1.4 倍。

在Intel 3之后,英特尔的Intel 20A(2nm)将迎来Angstrom时代,利用GAA(RibbonFET)晶体管和PowerVia技术提高功率保持能力。英特尔的竞争对手台积电将在 2025 年采用其2nm 节点的 GAA,在芯片制造商遇到小型化极限时让前者*一步。

与 4nm 和 3nm 一样,不同的团队也将设计20A 和 18A 节点,以实现更快的部署。20A 将为 Arrow Lake 供电,而 18A 将(可能)用于 Lunar Lake 的制造,这是英特尔客户端 CPU 架构的*次重大改组。如果英特尔的路线图成功,届时它将从其中国台湾竞争对手手中夺回工艺领导地位。

能如愿以偿吗?

虽然英特尔信心满满,且他们在工艺制程方面也是进步显著。但semiwiki重申:“我们相信英特尔能够在代工厂苦苦挣扎的时候显著加快他们的工艺开发。虽然我们不期望英特尔在研究的时间段内重新获得密度*优势,但我们相信他们可以重新夺回性能*优势。”

而在笔者看来,在先进制程代工成本越来越昂贵的当下,英特尔的入局,会给客户提供更多的筹码?尤其是在技术演进缓慢的当下,芯片巨头必将迎来他们的翻盘契机。这在他们下注RISC-V,拥抱Chiplet,以及发力先进封装之后,让人更有信心。

总之,先进芯片代工,不再是两个厂商的战役。

【本文由投资界合作伙伴微信公众号:半导体行业观察授权发布,本平台仅提供信息存储服务。】如有任何疑问,请联系(editor@zero2ipo.com.cn)投资界处理。