”ZedBoardにキャラクタ・ディスプレイ・コントローラを追加する4(ChipScopeデバック1)”の続き。

前回、ディスプレイにキャラクタの表示が出ないというバグで悩んでいたが、バグが解消してキャラクタがディスプレイに表示できるようになった。

バグは何だったかというと、CharDispCtrler.v のところでVGA信号の出力ポートにつないでいるVerilogコードがあった。それを下に示す。

assign VGA_RED = {red_node,0};

assign VGA_GREEN = {green_node,0};

assign VGA_BLUE = {blue_node,0};

red_node, green_node, blue_node は3ビット長の信号で、それを4ビット長のVGA_RED, VGA_GREEN, VGA_BLUE に接続するために下に1ビットの0を付けるはずだったのが、0と書いてしまったので、32ビット幅に拡張されてしまったようだ。それで、VGA_RED, VGA_GREEN, VGA_BLUE はいつでも0になってしまった。これを下のように書きなおした。

assign VGA_RED = {red_node,1'b0};

assign VGA_GREEN = {green_node,1'b0};

assign VGA_BLUE = {blue_node,1'b0};

これで、論理合成、インプリメントを行い、ハードウェアをSDKにエクスポートしてやってみるとディスプレイに文字が表示された。

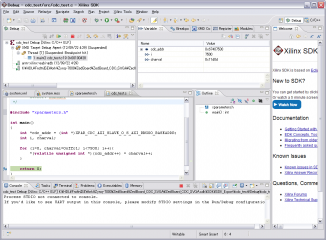

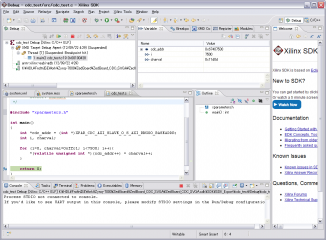

表示したプログラムを下に示す。

#include "xparameters.h"

int main()

{

int *cdc_addr = (int *)XPAR_CDC_AXI_SLAVE_0_S_AXI_RNG00_BASEADDR;

int i, charval;

for (i=0, charval=0xffc1; i<7500; i++){

*(volatile unsigned int *)(cdc_addr++) = charval++;

}

return 0;

}

注:キャラクタのデータ (chaval) のフォーマットは、15ビット目~13ビット目の3ビットがRedの明るさ、12ビット目から10ビット目の3ビットがGreenの明るさ、9ビット目から7ビット目の3ビットがBlueの明るさ、6ビット目から0ビット目の7ビットがアスキー・コードです。

charval = 0x41; にして、'A'を表示しようとしても、RGBの値が0なので表示しません。RGBの明るさも設定して下さい。

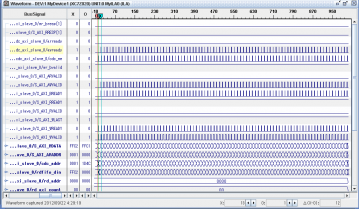

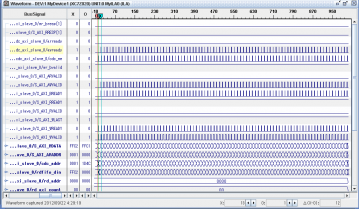

同時にChipScopeもS_AXI_AWVALID でトリガをかけてあった。ChipScope Analyzer Pro のWaveform ウインドウを下に示す。

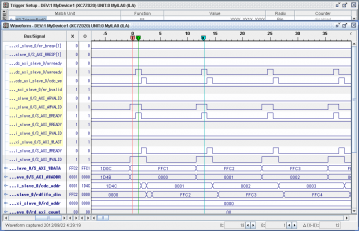

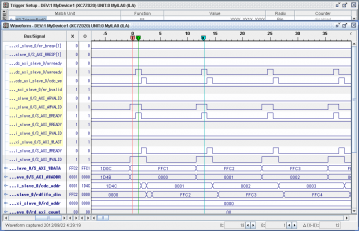

さすが、667MHzのARM9でバスアクセスを出しているだけあって、Writeアクセスが密に並んでいる。今度は前の部分を拡大してみた。

AXI4バスのWriteアクセスの間隔は12クロックだった。クロックは100MHzなので、1クロックは10nsec、12クロックで120nsec 間隔でWriteしている。

もし需要があれば、GitHub辺りにプロジェクトを置いておこうかと思いますが、需要はありますか?

(追加)GitHubは設定が難しかったので、YahooボックスでISE14.2 ZedBoard用のキャラクタ・ディスプレイ・コントローラIPを公開します。その他の設定はブログの通りに設定してください。なお、保証はありません。自己責任でお使いください。ダウンロードして動かした方は動作したかどうか?などの感想をコメントで教えて下さい。

(2012/10/01:追記)

コメントされた方はダウンロードされたと思うので、YahooボックスのISE14.2 ZedBoard用のキャラクタ・ディスプレイ・コントローラIPのリンクを削除しました。コメントが無いのが寂しいです。

(2012/10/14:追記)

キャラクタ・ディスプレイ・コントローラIPの情報は全て公開してあると思いますが、

IPとしてフォルダごと欲しいという方は使用したい理由を書いて、ご連絡ください。(理由は興味があるからとかでもOKです)

- 2012年09月22日 05:09 |

- ZedBoard

-

| トラックバック:0

-

| コメント:6

公開されたデータで試しました。あっさり動きました。今後、自作回路の接続の時には、手順を参考にさせていただこうと思います。ありがとうございました。

9/29のコメントで示したように、XPS単独で使いChipScopeは試していません。XPS単独だと、例えばディスプレイ・コントローラの内部信号を観測しようとしてもできないですよね。やはりバージョンアップに期待するしかないのでしょうか。

一か所だけつまずいたのは、手順12で、外部出力の信号名をデフォルトのままにして、コンパイルエラーを起こしたことです。久しぶりに使ったXPSなので、勘が鈍っていただけですが。

- 2012/10/01(月) 11:56:53 |

- URL |

- K林 #-

- [ 編集 ]

コメントありがとうございます。動いて良かったです。AXI4ネイティブ対応IPでした。XPS上でChipSopce コアを接続してみてはいかがでしょうか?

- 2012/10/01(月) 12:06:39 |

- URL |

- marsee #f1oWVgn2

- [ 編集 ]

HDMI出力できました。

色々アドバイス頂きありがとうございます。

実際に動くと楽しいですね。

続いてAXIスレーブのキャラクタディスプレイコントローラに挑戦しています。

HPにて公開されているCharDispCtrler.vでは合成できなかったので

想定しながら修正してSynthesisは通ったのですが、Translateにて

以下エラーが出てしまいました。

他に何か修正しないといけないところがあるのでしょうか?

[NgdBuild 604] logical block 'system_i/cdc_axi_slave_0/cdc_axi_slave_0/rdfifo' with type 'afifo_sm' could not be resolved. A pin name misspelling can cause this, a missing edif or ngc file, case mismatch between the block name and the edif or ngc file name, or the misspelling of a type name. Symbol 'afifo_sm' is not supported in target 'zynq'.

- 2013/01/11(金) 17:20:59 |

- URL |

- tattsuu #-

- [ 編集 ]

1.affio_sm をZynqのプロジェクトで再生成しているでしょうか?

2.afifo_sm.vhd (.vでも良いと思う)をVHDL(Verilog)フォルダに入れて、.pao ファイルにエントリを追加していますか?

lib cdc_axi_slave_v1_00_a cdc_axi_slave.vhd vhdl

lib cdc_axi_slave_v1_00_a afifo_sm.vhd vhdl

lib cdc_axi_slave_v1_00_a CharDispCtrler.v verilog

lib cdc_axi_slave_v1_00_a char_gen_rom.v verilog

lib cdc_axi_slave_v1_00_a disp_timing.v verilog

lib cdc_axi_slave_v1_00_a frame_buffer.v verilog

3.afifo_sm.ngc も エントリを.bbd ファイルに追加して、実体を netlist フォルダに入れていますよね?

これでダメな場合は、Zedboard用のキャラクタ・ディスプレイ・コントローラIPを送りますので、ブログに指定のメールアドレスにメールください。その代わりと行ってはなんですが、レポートお願いします。

- 2013/01/11(金) 19:57:01 |

- URL |

- marsee #f1oWVgn2

- [ 編集 ]

ご指摘いただいた通りすでに対応いたしましたが、

残念ながら動いていない状況です。。。。

もし可能であればお暇なときにIPを送っていただけますか?

もちろんレポートは出させていただきます。

よろしくお願いしますm(_ _)m

メールアドレスはコメント記載の欄を参照ください。

- 2013/02/01(金) 13:53:08 |

- URL |

- tattsuu #-

- [ 編集 ]

残念ながら諸事情によりIPの提供を中止いたします。再開する場合はコメント欄で連絡いたします。

- 2013/02/02(土) 00:05:00 |

- URL |

- marsee #f1oWVgn2

- [ 編集 ]