Zynq-7000シリーズのxc7z020clg484-1を使用した

ZC702ボードを残念ながら持ってはいないのだが、チュートリアルの”

Zynq-7000 EPP Concepts, Tools, and Techniques A Hands-On Guide to Effective Embedded System Design UG873 (v14.1) May 31, 2012”を見つけたので、実機で試す部分を抜いて、やってみることにした。Zynq-7000の雰囲気だけでも味わってみようという企画だ。ISE14.1を使用しているが、確かISE14.1 WebPACKでも実行可能だと思う。

それでは、ZC702ボードのPlanAheadプロジェクトを作るところから始めよう。

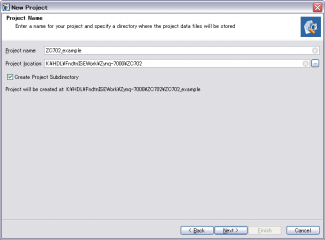

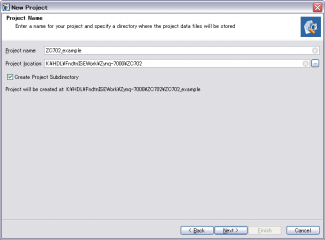

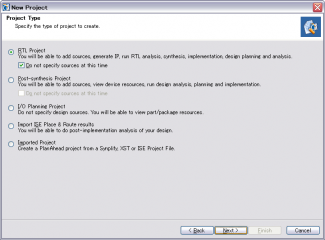

・PlanAheadを立ちあげて、Create New Project をクリックし、New Projectウィザードを立ち上げる。

・Project name はZC702_example とした。Project location を設定した。

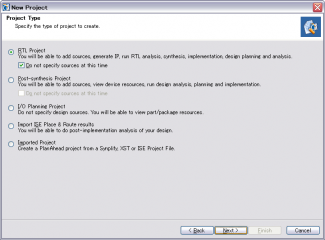

・Project Type はRTL Project を選択した。

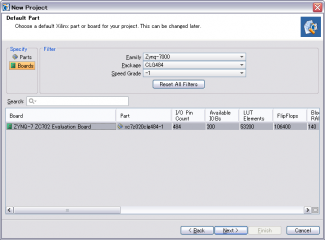

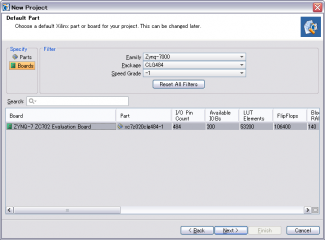

・FPGAチップかボードを選択する。Specify でBoards を選択し、Family からZynq-7000 を選択すると、今のところ選択できるのは、ZC702 Evaluation Board のみだ。

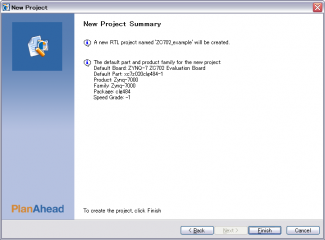

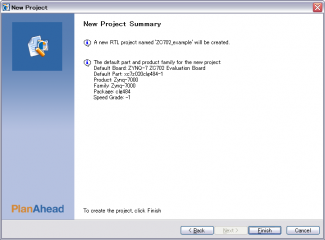

・New Project Summary が出て、Finishボタンをクリックした。

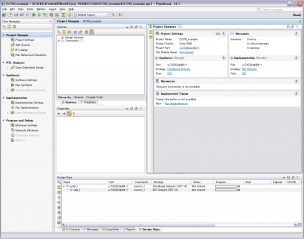

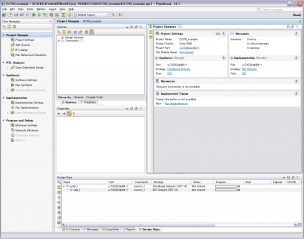

・PlanAheadのプロジェクトが出来上がって、PlanAheadが立ち上がった。

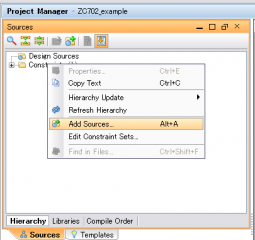

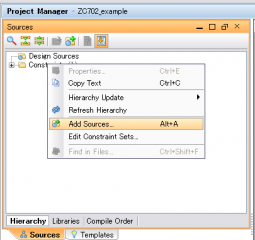

・Project Manager のSourcesウインドウで右クリックメニューからAdd Sources... を選択する。

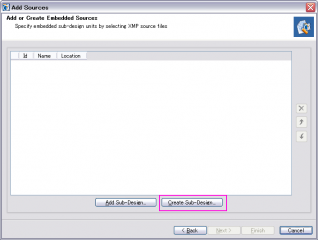

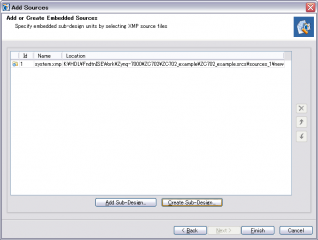

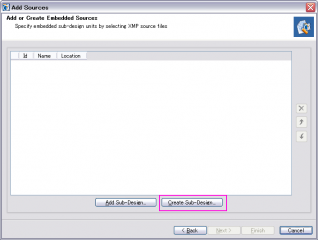

・Add or Create Embedded Sourcesを選択した。

・Create Sub-Design をクリックした。

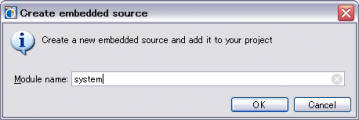

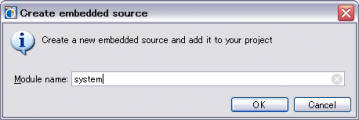

・Module name にsystem と入力した。

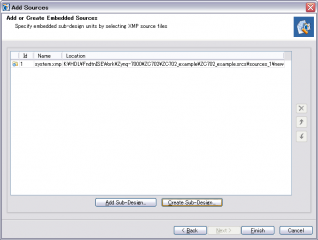

・system.xmp がエントリに入った。Finishボタンをクリックした。

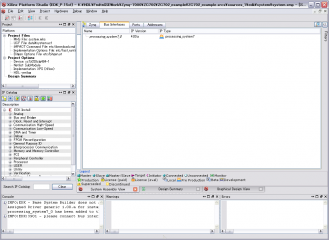

・XPSが立ち上がって、Platform Studio のダイアログが出た。Processing System7 をシステムに加えるか?と聞いてきたので、Yesボタンをクリックした。

・XPSが立ち上がった。Bus Interface タブをクリックすると、Processing System7が入っているのがわかる。

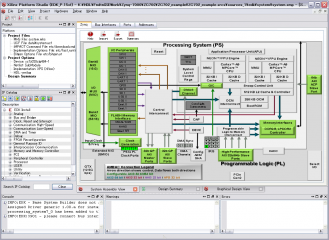

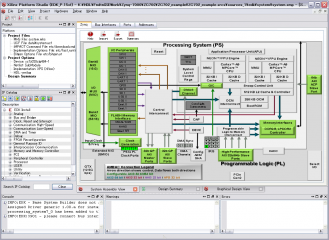

・Zynq タブをクリックすると、Processing System(PS) のブロック図が見えた。

”

Zynq-7000(ZC702)のチュートリアルをやってみた2(XPS、SDK)”に続く。

- 2012年06月21日 05:31 |

- Zynq

-

| トラックバック:0

-

| コメント:0